ISE Design Suite - 3. Download verification is only supported with Google Chrome and Microsoft Internet Explorer web bowsers. All Platforms ZIP - To install, extract the zip to a temporary location and run 'xsetup. Archives Downloads are not maintained. Modelsim XE Libraries - 7. Xilinx ISE [2] I ntegrated S ynthesis E nvironment [3] is a software tool produced by Xilinx for synthesis and analysis of HDL designs, enabling the developer to synthesize "compile" their designs, perform timing analysis , examine RTL diagrams, simulate a design's reaction to different stimuli, and configure the target device with the programmer.

| Uploader: | Akigor |

| Date Added: | 1 February 2010 |

| File Size: | 34.6 Mb |

| Operating Systems: | Windows NT/2000/XP/2003/2003/7/8/10 MacOS 10/X |

| Downloads: | 87637 |

| Price: | Free* [*Free Regsitration Required] |

Designers targeting families other than Virtex-6 or Spartan-6 do not need to install At the end of installation, you will receive an error about fileset. Documentation Navigation Standalone - Modelsim XE Libraries - 7.

ISE Foundation - ChromeFirefoxInternet Explorer 11Safari. The low-cost Spartan family of FPGAs is fully supported by this edition, as well as the family of CPLDsmeaning small developers and educational institutions have no overheads from the cost of development software.

ISE Design Suite

All Platforms ZIP - 1. Speedfile Update - Linux ZIP - ChipScope Pro - 9. Embedded Development Kit - If you have trouble downloading large files, try the new multiple file download above.

We strongly recommend to use the web installers as it reduces download time and saves significant disk space. Japanese Documentation Update - Device Support - 9. The IP Update 2. Prior to installing IP Update 3, please read Answer For Service Pack release notes and installation instructions, please read Answer Record To install, extract the zip to a temporary location and run 'xsetup.

Turn off virus scanner to reduce installation time. Archived from the original on October 7, ISE Foundation - 5.

ChipScope Pro - IP Cores are offered xilihx Xilinx and other third-party vendors, to implement system-level functions such as digital signal processing DSPbus interfaces, networking protocols, image processingembedded processorsand peripherals. Embedded Development Kit - 7. Smart Models - 7.

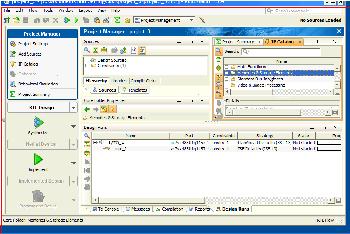

Please follow these Installation Instructions. Release Notes What's New in Vivado. The Design hierarchy consists of design files moduleswhose dependencies are interpreted by the ISE and displayed as wrbpack tree structure.

XUP Students

After downloading, unzip the file and run "setup". Retrieved 8 May ISE Design Suite - The Transcript window provides status of currently running operations, and informs engineers on design issues.

Architecture Support and Requirements: 1.4 from the original on March 3, If you purchased a new license or license renewal, please obtain your registration ID from the Xilinx Answer

Comments

Post a Comment